|

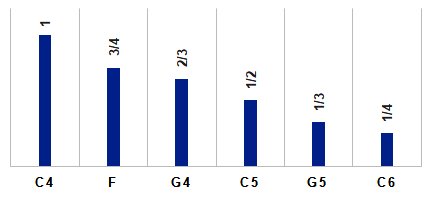

Adding a third stage would even further aggravate this situation. But this decreases the available amplitude for the amplified signal. However since the base voltage of the second stage is taken from the collector of the first stage it is inherently larger that the first stage base voltage, and the second stage collector voltage is still higher. To avoid saturation the collector voltage of each stage must be greater than the base voltage, enough greater to allow for the collector voltage signal swing. The rationale behind a complementary pair cascade is a problem that can arise with a cascade of similar n-type stages. This happens at the cost of overall signal gain in the combined amplifier.įigure 10.1.4 complementary cascade amplifierĪ two-stage 'Complementary Pair' BJT amplifier circuit diagram is shown in figure 10.1.4.

The R 3, R 4resistor divider in figure 10.1.2 not only reduces the signal amplitude seen at the base of Q 2, it also reduces the DC bias level from the collector of Q 1 to a more manageable DC level at the base of Q 2. If this voltage “stacking” is severe, little head room is left in the final stages of the cascade. In DC coupled multistage cascaded common emitter amplifiers the output bias level of each stage increases to maintain the collector more positive than the base (constant current operation). The second way includes inter-stage loading as an input divider in the gain of the second stage while the first way includes it as an output divider in the gain of the first stage. In this case, the first-stage gain output quantity is the Thevenin equivalent voltage, not the actual collector voltage of the amplifier with the second stage connected. Then the Thevenin equivalent output of the first stage is connected to the input of the second stage and its gain is calculated, including the input divider formed by the first-stage output resistance and second-stage input resistance. Second way: the first-stage gain is found by disconnecting the input of the second stage, thereby eliminating output loading. Because the loading (R 3,R 4 output divider) was accounted for in the first-stage gain, the second-stage gain input quantity is the Q 2 base voltage, v B2 = v o1. Then the second-stage gain is calculated from the collector of Q 1 which is the output of the first stage. First way: the gain of the first stage is calculated including the loading of the R 3,R 4 resistor divider. The total voltage gain can be calculated in either of two ways. Because the input resistance of the second stage (resistors R 3 and R 4) forms a voltage divider with the output resistance (R C1) of the first stage, the total gain is not simply the product of the gain for the individual (separated) stages. Two cascaded common emitter stages are shown in figure 10.1.2. The complication in calculating the gain of cascaded stages comes from the non-ideal coupling between stages due to loading. We generally refer all noise to the input of the signal chain, taking out the effects of the gain stages.ġ0.1 Cascade of two single transistor stagesįigure 10.1.2 DC coupled Common Emitter stages Even if AC-coupled, noise from preceding stages gets amplified by each downstream amplifier stage, making for nothing but a noise source after a while.

There are practical reasons why you just can't continue cascading stages “forever…” If DC-coupled, real-world offsets can be impossible to trim out. By the time you reached that point, other adverse effects would have caused much more trouble, for example, the fact that noise from each successive stage is added to the noise coming into that stage and is further amplified on down the cascade of amplifiers. In fact, you would have to go to a cascade of 100 stages with these specifications before you even lost 1% of the expected ideal gain ( i.e. To confirm this assertion, assume a low performance op amp with R out = 100Ω and R in = 1MΩ, what is the gain with two stages of gain A 1 and A 2 in series? (assume R L = 1 MΩ)

That effect, if any, is modeled in the R out.įor most integrated circuit amplifiers where R in is in the MΩ to GΩ range, and R out is in the 50 to 100 Ω range, the gains are pretty close to being the simple product of the gain stages. The above equations assume that the individual amplifier gains, A do not change with output loading. As a matter of fact, we really only need R out to go to 0 to have the resistor dividers to go to 1. As we would expect, the overall equation reduces to the ideal case of A V = A 1*A 2 for two ideal stages when we let the R out go to 0 and the R in go to infinity.

0 Comments

Leave a Reply. |

RSS Feed

RSS Feed